通常将指令执行过程中数据所经过的路径,包括路径上的部件称为数据通路。ALU、通用寄存器、状态寄存器、cache、MMU、浮点运算逻辑、异常和中断处理逻辑等都是指令执行过程中数据流经的部件,都属于数据通路的一部分。通常把数据通路中专门进行数据运算的部件称为执行部件或功能部件。数据通路由控制部件进行控制。控制部件根据每条指令功能的不同生成对数据通路的控制信号,并正确控制指令的执行流程。

数据通路中信息的流动的特点:①每条指令在取指令阶段和指令译码阶段都一样;②每条指令的功能不同,故在数据通路中所经过的部件和路径可能不同;③数据在数据通路中的流动过程由控制信号确定;④控制信号由控制器根据指令代码来生成。

二、数据通路的基本结构

数据通路的基本结构主要有以下两种:

1. CPU总线方式

CPU内部单总线方式:将所有寄存器的输入端和输出端都连接到一条公共的通路上,这种结构比较简单,但是数据传输存在较多的冲突现象,性能较低。如果连接各部件的总线只有一条,称为单总线结构;如果CPU中有两条或更多的总线,则构成双总线结构或多总线结构。例如,CPU内部三总线方式,是将所有寄存器的输入端和输出端都连接到多条公共的通路上,相比之下单总线中一个时钟内只允许传一个数据,因而指令执行效率很低,因此采用多总线方式,同时在多个总线上传送不同数据,提高效率。

2. 专用数据通路方式

根据指令执行过程中的数据和地址的流动方式安排连接线路。避免使用共享的总线,性能比较高,但硬件量大。

二、试题再现

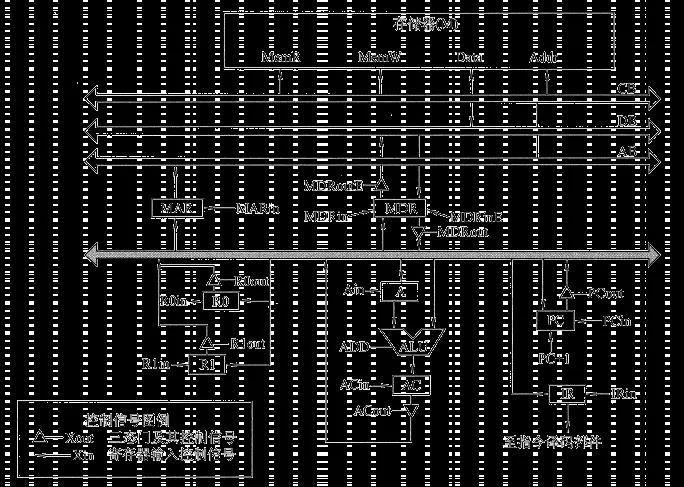

1. (2009-44)某计算机字长16位,采用16位定长指令字结构,部分数据通路结构如下图所示。图中所有控制信号为1时表示有效,为0时表示无效。例如,控制信号MDRinE为1表示允许数据从DB打入MDR,MDRin为1表示允许数据从内总线打入MDR。假设MAR的输出一直处于使能状态。加法指令“ADD (R1),R0;”的功能为(R0)+((R1))→(R1),即将R0中的数据与R1的内容所指主存单元的数据相加,并将结果送入R1的内容所指主存单元中保存。

下表中给出了上述指令取指和译码阶段每个节拍(时钟周期)的功能和有效控制信号,请按表中描述方式用表格列出指令执行阶段每个节拍的功能和有效控制信号。

题表5-1 指令取指和译码阶段每个节拍的功能和有效控制信号

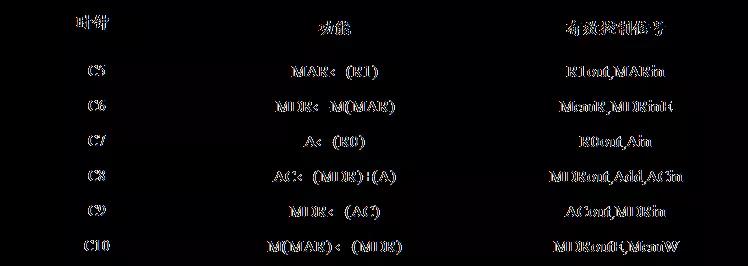

【答案】

指令执行阶段每个节拍的功能和有效控制信号如下所示。

表5-2 指令执行阶段每个节拍的功能和有效控制信号

由上表,若用最少的节拍,则C6和C7可以合并。考研实用工具推荐

1、2022考研院校专业匹配查询系统

2、近4年全国各在招院校专业复试分数线查询

3、历年调剂信息查询

4、历年各院校专业目录查询

5、历年各院校报录比查询

6、历年各院校参考书目录查询

免责声明:本站所提供的内容均来源于网友提供或网络搜集,由本站编辑整理,仅供个人研究、交流学习使用,不涉及商业盈利目的。如涉及版权问题,请联系本站管理员予以更改或删除。